Multisim Edu PLD 的使用#

之所以想要写这篇文档是因为有许多同学(包括我自己在内)都被误导,认为 Vivado 只能装在 C 盘内才可被 Multisim 识别。这在我之前的有关于 Multisim 的安装的文档中讲到过。其实装在 C 盘说可以让 Multisim 自动识别到 Vivado,我们其实可以手动指定 Vivado 的位置。这篇文档将会从 Multisim 进行 basys3 FPGA 开发板实验讲起。

省流:Vivado 是可以装在 C 盘以外的盘的。不需要专门为 C 盘扩容去安装几十个G的Vivado

假如你不会 Multisim PLD 的使用建议从头阅读,假如你熟悉使用,就是想知道 Vivado 装在 C 盘以外的盘如何处理,直接跳至末尾看 Vivado 不在 C 盘即可 即可。

Multisim PLD 的操作流程#

操作环境#

操作系统:Windows 10

容量:40 个 G 起步(Vivado 2018.3)

软件:Multisim 14.2 Edu,Vivado 2018.3

同样不推荐 Mac 用户。Mac 用户另请高明,或者老老实实使用实验室电脑。

建立项目#

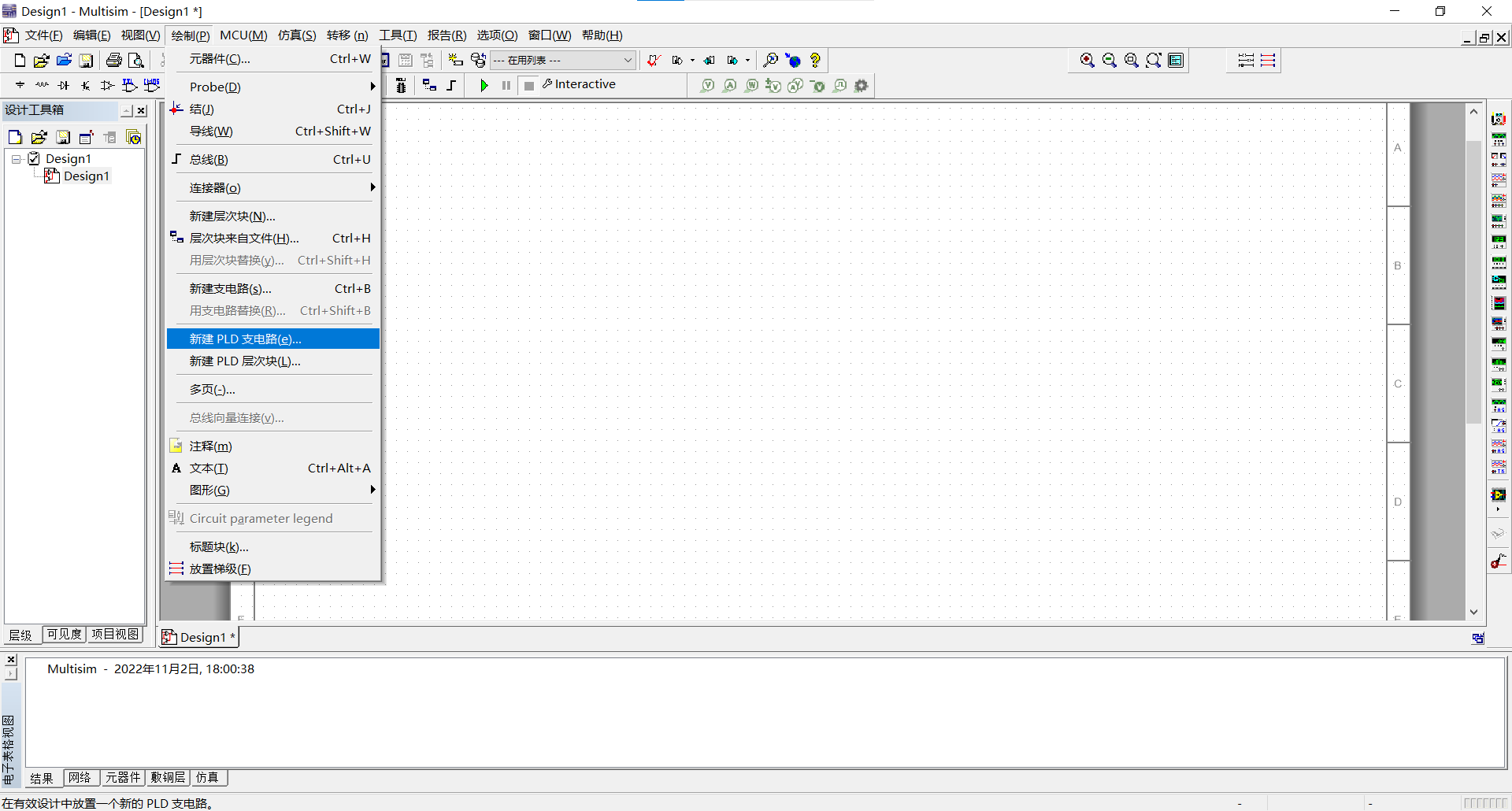

新建一个 Multisim 项目,如图选择新建 PLD 支电路。

一般都建议选支电路不要选层次块。以及后续开发在 PLD 模块中自己搭建模块时也用支电路而不用层次块。具体原因为支电路仅仅在这个工程内有效。而如果想在其他工程中使用其实可以通过简单的复制粘贴过去,此时两个工程间的两个模块互不映像。而如果选用层次块,层次块自己创建一个文件与之对应,修改这个层次块会修改这个文件。此时如果两个工程用同一个层次块,这边修改,另外一边也会跟着修改。除非你的模块已经做的非常好了,在每个工程中都能用,且保证自己不会去修改它。就像 C 语言中的库函数一样,你不会去改库函数。但考虑到大家的时间有限,很难自己能搭出一个万能的模块,还是建议大家用支电路,这个也允许在不同工程之间复制粘贴。

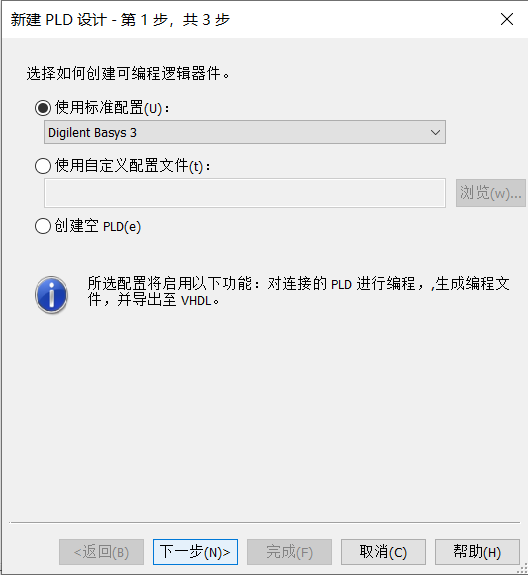

选择配置 —— basys3#

数字电路实验使用的时 Basys3 开发板,固定选择如图配置就行。后续还可以自定义 PLD 模块名称,选择 PLD 模块的 IO 口。在此不作展示。仅仅说明原理。

原理:Basys3 开发板上有许多引脚这些都是固定的,全都有自己的名字编号的。Multisim 中也存有 Basys3 的资料库,所以其直接提供好了那么多引脚,你只需要选择你需要的引脚即可。如 JB0,JB1,SW0,SW1,LED0,LED1等等。这些编号全都有其对应的外部设备对应(称为“外设”)。

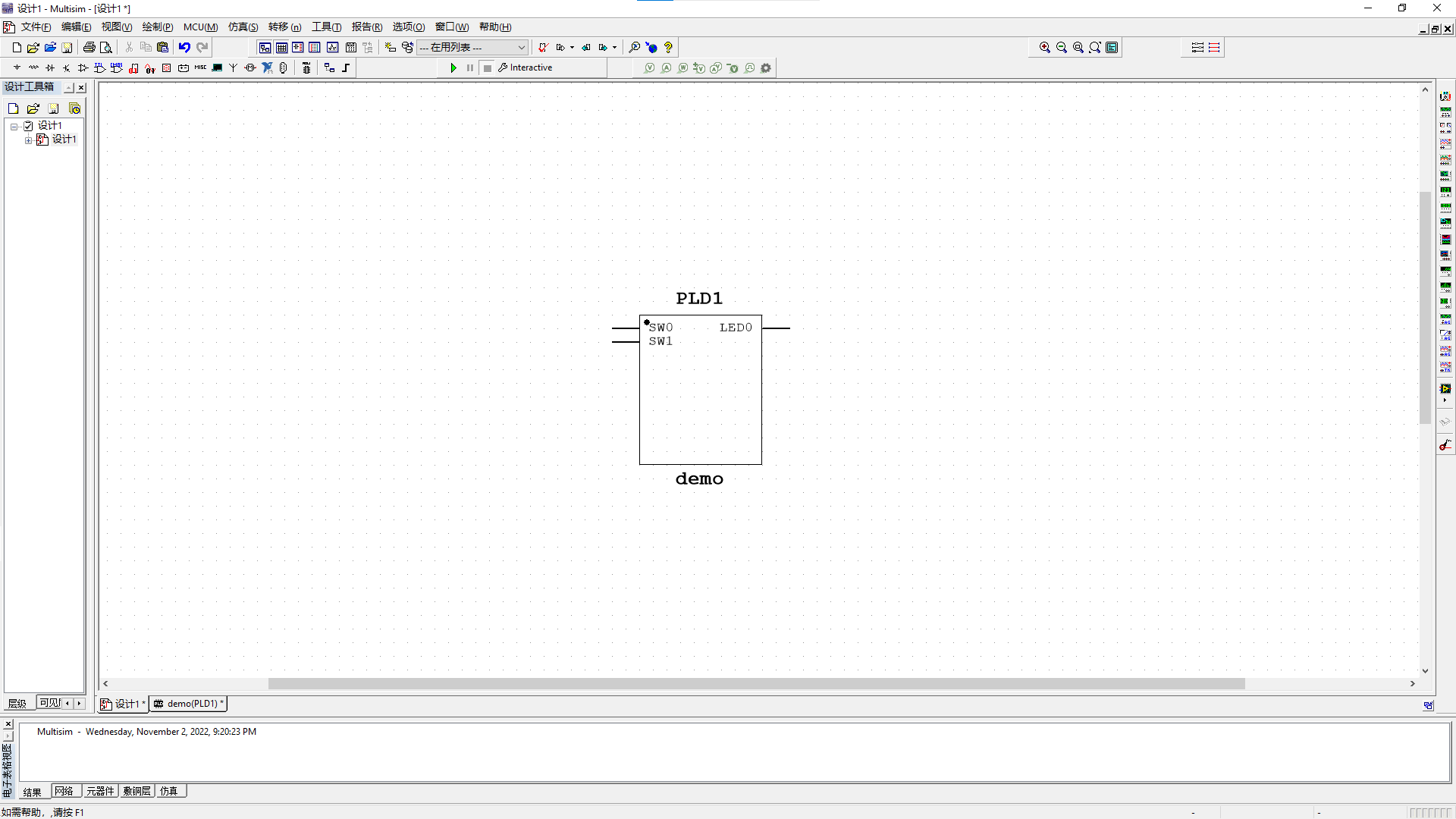

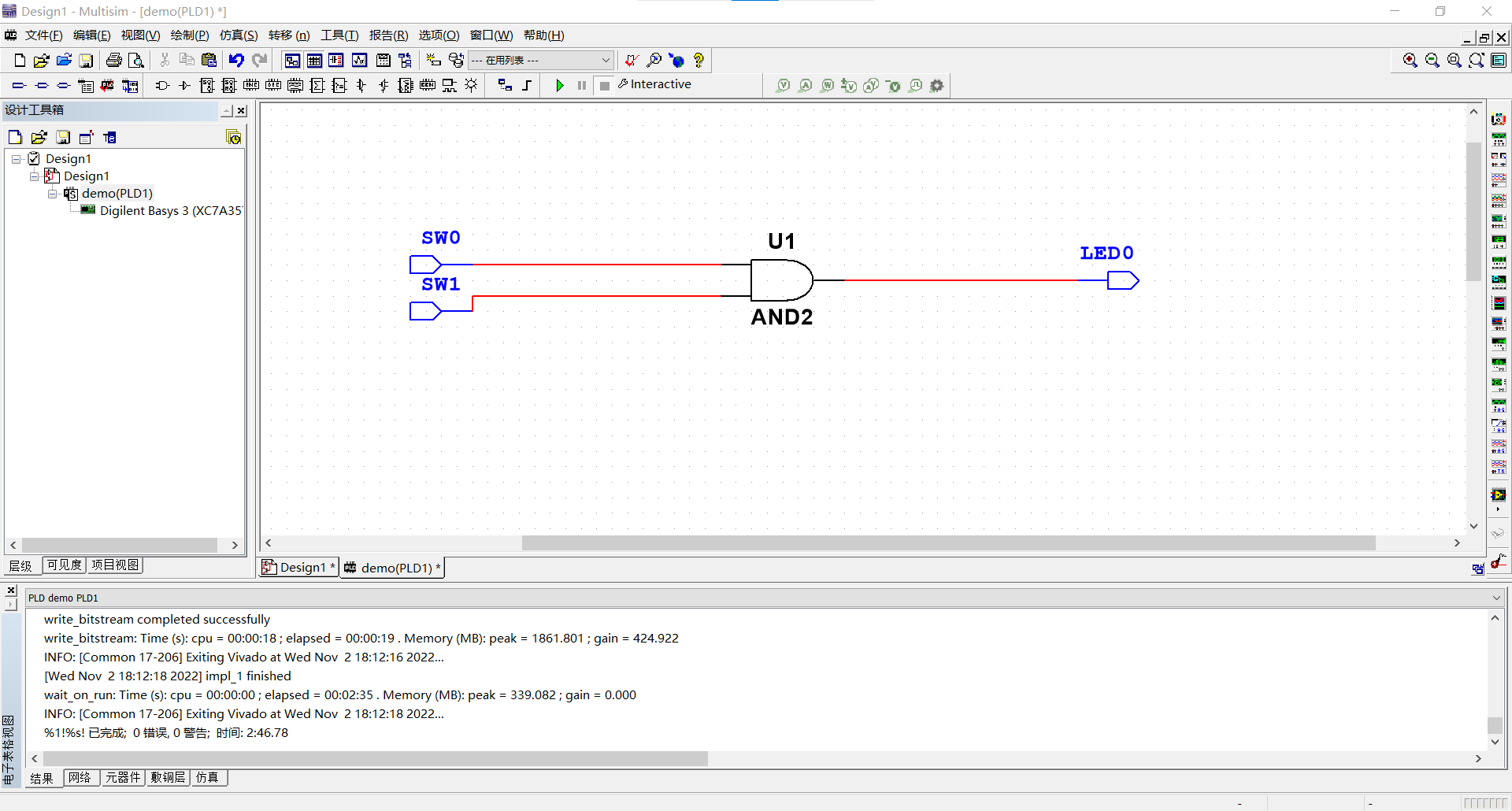

如下所示已经搭建好了一个 PLD 模块

搭建门电路#

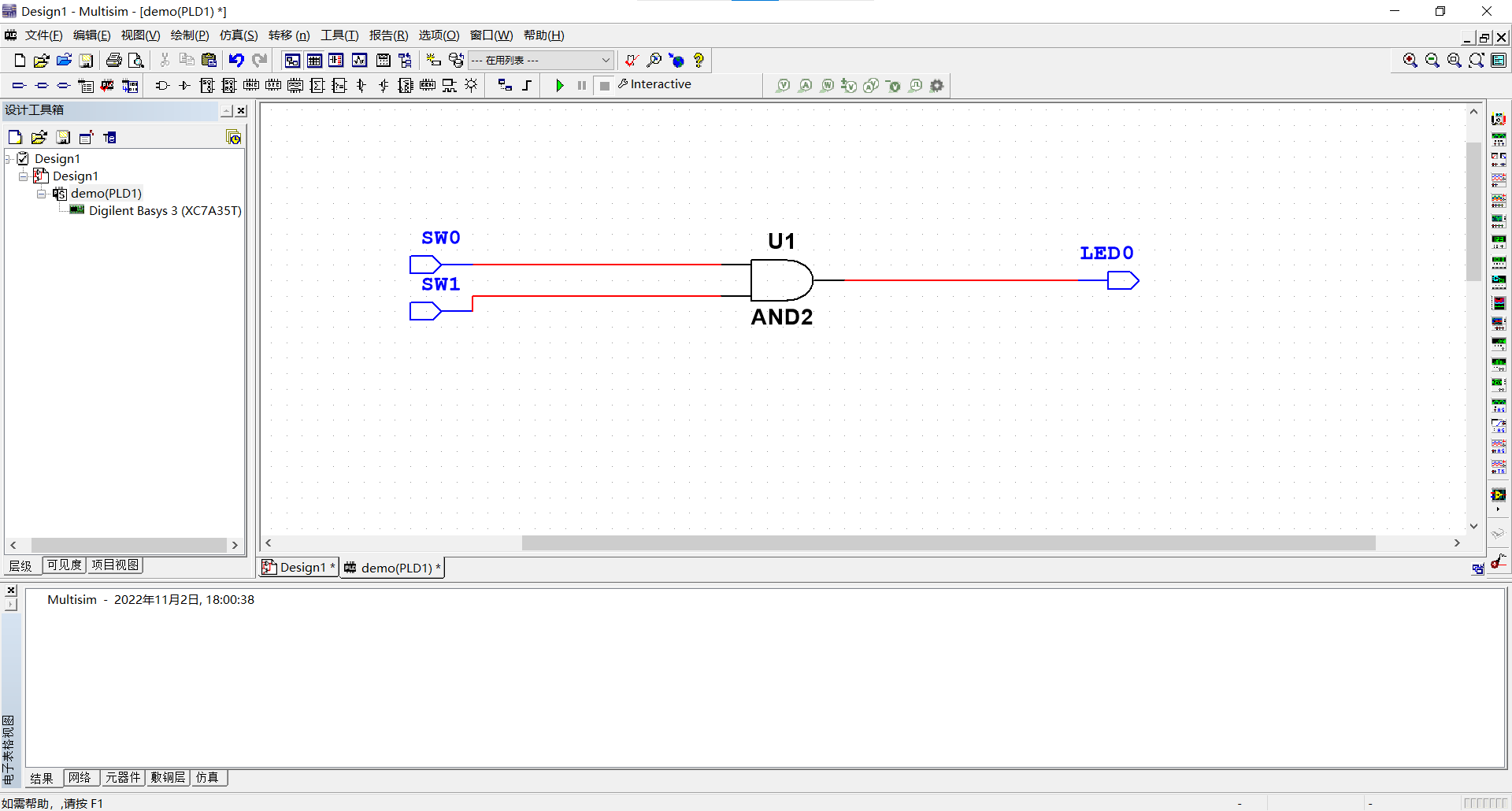

上述那个 PLD 模块其实就是 Basys3 开发板,我们需要在 Basys3 开发板里面搭建自己的逻辑电路,所以我们需要点进去这个模块,点进这个模块可以双击这个 PLD 模块然后点打开子电路,也可以将鼠标悬停在 PLD 模块上会在左上角出现一个小标志,点击这个小标志也能进去。当然也可以看左边的资源管理器视图,当前是 Design1,点击下面的那个 PLD 就可以进子电路了。

如上是已经在子电路里面并且搭建了一个简单的与门的逻辑电路。从拨码开关 SW0 和 SW1 读入电平信号,相与后输出至 LED0 对应的 LED 灯。

烧录成 bit 流#

前面都很简单相当于是废话,这里才是重中之重,误导了一批又一批人,包括我在内,包括实验中心老师在内。

将这个逻辑电路烧录成硬件可读取的 bit 流,才可被 Basys3 开发板运行。这里的操作是要去后台调用 Vivado。

然后悲剧的是曾经一度以为 Vivado 只能在 C 盘才可被 Multisim 识别。其实这句话应该被改为 Vivado 只有在 C 盘才可别 Multisim 自动识别。如下所示。操作如下。

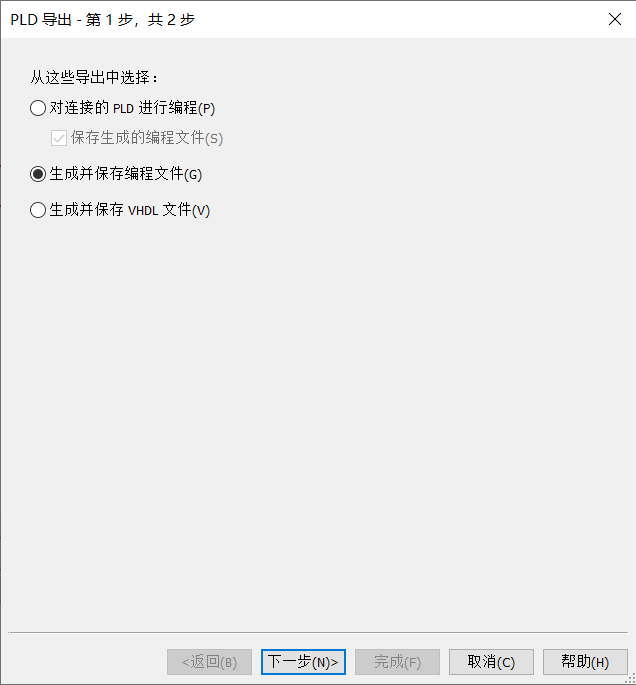

点击左上角的那个 导出至PLD 的小按钮。(鼠标悬停在这个按钮上会出现这个字样)点击之后出现如下界面

- 第一个选项的意思是生成 bit 流,同时将这个 bit 流烧录至开发板中(此时需要你的电脑已经连接了开发板,如果没连接则无法操作成功)

- 第二个选项的意思是只生成 bit 流,省去了烧录到开发板的过程,这时你的电脑不需要连接开发板也可生成 bit 流。

- 第三个选项不重要,至少我都没用过。。。。

在该演示中因为没有开发板,所以这里选择第二个。接下来进入到了最重要的下一步。

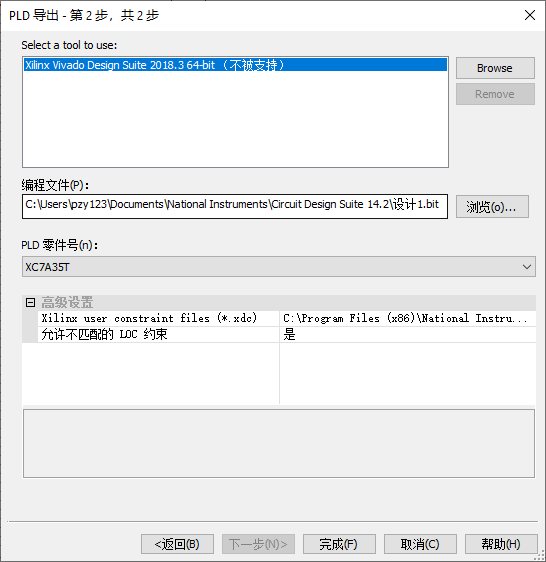

以下是 Vivado 装在 C 盘的情况。

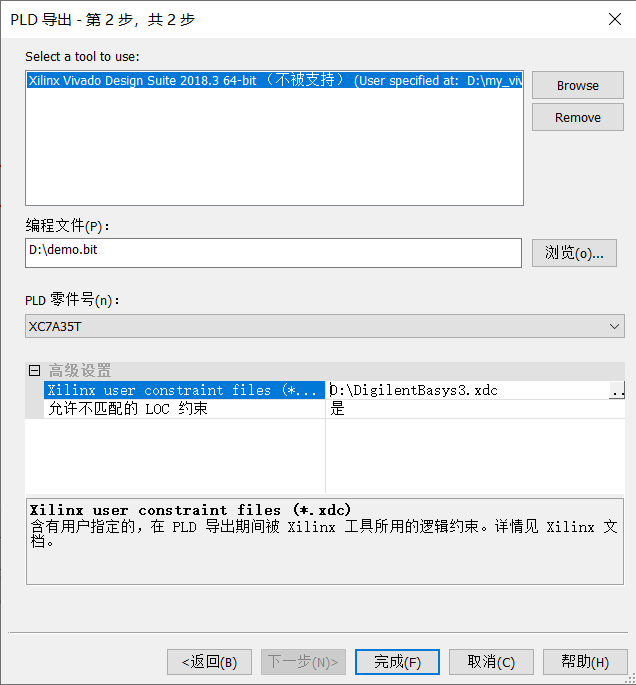

可以看见这里识别出来了 Vivado,但这里有个(不被支持)字样。注意,在我看来,这应该是个bug,其实这个不被支持并不影响使用,忽视即可。

下面的那个编程文件就是输出的 bit 流文件,可以自定义名称和地址。

再下面的这个高级设置要注意。这里有个 Xilinx user constraint files(*.xdc) 的选项。可以看出他需要一个 xdc 后缀的文件。这个文件一般是在 Multisim 的安装目录下。进入你的目录,我这里的默认目录是

C:\Program Files (x86)\National Instruments\Circuit Design Suite 14.2\pldconfig。就是在这个 pldconfig 目录下,有这些 xdc 文件。这里是使用 Basys3 开发板,故选择 DigilentBasys3.xdc 这个文件。

注意,这个文件一般是默认配置好的,但也会,并且是经常会出现弄错的情况,或者这一栏是空的,这时候就需要去自己去手动选择,点击右边,点击那三个小点,可以打开文件资源管理器,选中对应 xdc 文件即可。

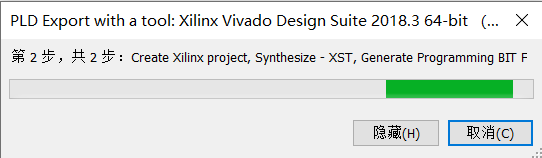

下面这个是点击完成后出现的正在处理计算的界面。这里是 2 步,如果你之前选择了第一个选项则是 4 步。

这里成功生成,可以看到左下角显示 0 错误 0 警告。代表已经成功生成了 bit 流

此时便可在对应的路径下找到这个 bit 流文件

这样一套下来点击完成就可以去烧录了。再看接下来的情况,是 Vivado 不在 C 盘的情况。

Vivado 不在 C 盘#

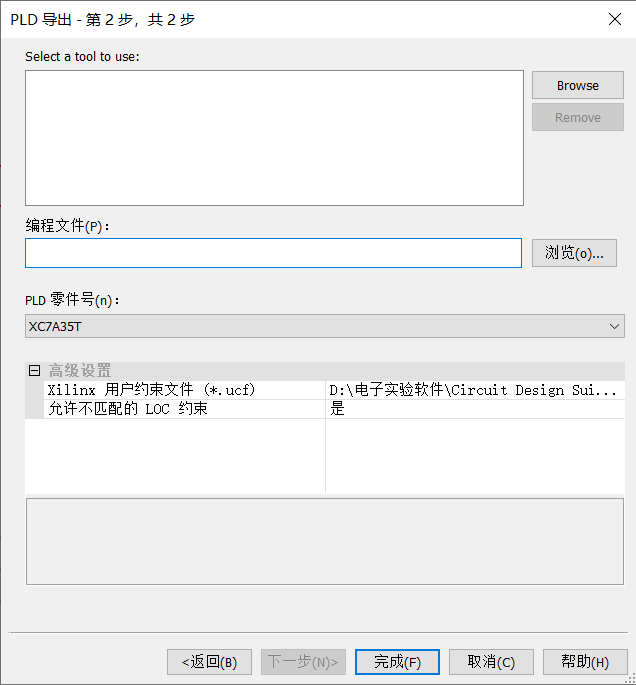

Vivado 不在 C 盘时这个界面如下,没有识别到 Vivado。此时可以手动添加。

点击右边这个 Browse,选择 Vivado 所在的目录。这里以 Vivado2018.3 举例(推荐搭建安装2018.3的版本,只有40个G,且也能完成任务)

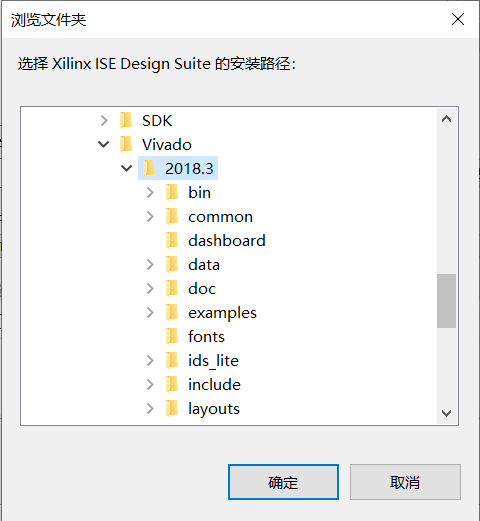

选中 Vivado 对应的版本的那个文件夹就行。如下所示。选中这个 2018.3 的文件夹即可。点击确定即可成功找到

成功添加后如下所示,显然与之前自动识别出来的效果一样,虽然还有一个不被支持字样。但可以看见后面有个 User specified,代表是我们指定的。不是 Multisim 自己找到的。两者没有任何差别。

注意(很重要):这时候眼尖的小伙伴就发现了,这里 .xdc 文件怎么在 D 盘里面啊。这是因为这个素材来自另外一台电脑,这里的截图素材并不完全来自同一台机子。这里的情况是因为这个 xdc 文件路径里面带有中文,也就是说,Multisim 并没有装在默认位置,而是装在了自定义的文件夹里,而且这个文件夹带有中文(太悲催了,buff 叠满了)。这时候就无法读取,需要另外新开一个无中文的路径,把 xdc 文件拷贝过去。

总结#

以上就是这么多。总共分为以下几点

- Multisim PLD 的使用教程(比较简单)

- 可以只生成 bit 流而不写入开发板

- Vivado 也可以不装在 C 盘(重要)

- xdc 文件不能有中文路径(重要)

祝大家数电实验愉快!

附上我的邮箱:201180070@smail.nju.edu.cn